Dazu sind Modifikationsroutinen, Verifikationstätigkeiten und die abschließende Beurteilung der FuSi in den Sicherheitslebenszyklus zu integrieren. Jede Phase ist zu beschreiben mit Ziel, Anwendungsbereich, den notwendigen Eingangsinformationen und den dokumentierten Ergebnissen der Phase. Weiterhin ist der Bezug zu den Anforderungen der Norm notwendig, um deren Ziele strukturiert umzusetzen.

Oft wird die FuSi als V-Modell dargestellt und als unvereinbar mit agilen Vorgehensweisen wie Scrum interpretiert. Teilweise sind in bestimmten Phasen „Sprints“ tatsächlich möglich. Die Aufwände lassen sich dadurch nicht reduzieren und machen die Maßnahmen zur Vermeidung systematischer Fehler nicht gerade effektiver.

Ein Technisches Sicherheitskonzept beginnt mit der Anforderungsspezifikation an den Entwurf

Ausgehend von den Top-Level-Anforderungen an das sicherheitsbezogene E/E/PE-System werden Anforderungen an den Entwurf durch Zerlegung der Sicherheitsfunktion in Teilfunktionen und Zuordnung zu Teilsystemen oder Elementen hergeleitet. Dabei werden oft Blockdiagrammsequenzen wie Sensor(en), Logik(en) und Aktor(en) vollständig beschrieben. Es ist die Vor- und Rückverfolgbarkeit (Traceability) zwischen den Top-Level-Systemanforderungen und den Entwurfsanforderungen zu gewährleisten. Weiterhin sind neben der Sicherheitsfunktion – zerlegt in Teilfunktionen – auch Anforderungen zur Sicherheitsintegrität an Elemente im Hinblick auf Entwurf und Architekturmerkmale zu entwickeln. Nicht alle Anforderungen müssen Teil der Sicherheitsanforderungsspezifikation sein. Wenn Wechselwirkungsfreiheit gewährleistet ist, dann sind auch Nicht-Sicherheitsanforderungen innerhalb sicherheitsrelevanter Elemente abbildbar.

Je Sicherheitsfunktion sind Anforderungen an:

- alle beteiligten Elemente wie Teilsysteme/Hardware/Software zu stellen

- die Integration der Elemente

- Performance wie Rechenleistung, Reaktionszeit, Speicherkapazität, Kommunikationsraten usw…

- Sensoren, Steuerungen und Regelungen wie Genauigkeiten, Dynamik, Robustheit und Stabilität

- Schnittstellen (Userinterface, Inter- & Intra-System-Kommunikation, Energie, Mechanik, Umwelt (EUC), usw…)

- das Ausfallverhalten und Ausfallreaktion (z.B. Fail-Safe oder Fail-Silent)

- Wechselwirkungen zwischen HW und SW (z.B. Interrupt, POST usw…) sowie Wechselwirkungsfreiheit (z.B. Partition) sofern bereits bekannt

- die Spezifikation von Grenzwerten (Zeitbeschränkungen, Temperaturbeschränkungen, Schock…)

- Einschränkungen im Hinblick auf CCF (z.B. getrennt abgesicherte Schaltkreise)

- die Initialisierung und Neustart der Sicherheitsfunktion bzw. des Systems

Für die Sicherheitsintegrität und den zu erfüllenden Ausfallgrenzwert sind weiterhin folgende Anforderungen zu spezifizieren:

- Hardwarearchitekturvorgaben im Hinblick auf Fehlertoleranzmerkmale und/oder den Anteil sicherer Ausfälle (SFF) oder Zuverlässigkeitsdaten der Bauteile

- Testintervalle und anwendungspezifische Wiederholungstestintervalle

- Handlungen und Maßnahmen nach Detektion/Diagnose eines gefahrbringenden Ausfalles

- Wiederholungsprüfung, die Betriebsmittel dafür, die Funktionen der Prüfung und Einschränkungen

- Extrem-Umgebungsbedingungen [Temperatur, Feuchte, elektrisch, mechanisch] für alle Lebenszyklusphasen [Herstellung, Lagerung, Prüfung, Transport, Installation, Inbetriebnahme, Betrieb und Instandhaltung]

- Elektromagnetische Störfestigkeit (IEC 61000-1-2 / 5-7) und sonstige Einflüsse dieser Art

- Leistungsvermögen der Betriebsmittel

- Kontrollmaßnahmen zur erforderlichen Qualität

Verfahren und Maßnahmen zur Vermeidung von Fehlern

Die Phase der Spezifikation an den Entwurf des sicherheitsbezogenen E/E/PE-Systems ist erfahrungsgemäß eine Fehlerquelle und wird i.d.R. mit einer ausgewählte Gruppe von Verfahren und Maßnahmen behandelt. Diese sind im Anhang B des 2. Teils in Tabelle B.1 mit Richtliniencharakter enthalten für jeden Sicherheitsintegritätslevel (SIL 1 bis 4) mit unterschiedlicher Wirksamkeit entweder verbindlich oder mit Empfehlungsgraden von „besonders Empfohlen“ bis hin zur „ausdrücklichen Ablehnung“.

Verbindlich für alle SIL sind:

- ein Projektmanagement

- eine Dokumentation

Quasi verbindlich durch „besonders empfehlenswert“ ist:

- die Trennung von Sicherheitsfunktion und anderen Funktionen

- Strukturierte Spezifikation

- Inspektion / Prüfung der Spezifikation

Verifikation der Anforderungsspezifikation an den Entwurf

Durch Verifikation muss die Angemessenheit der Anforderungsspezifikation im Hinblick auf die Sicherheit, Funktionalität und planungsspezifische Sicherheit festgestellt werden. Dabei ist im Wesentlichen auf Widersprüche zu prüfen im Hinblick auf die Sicherheitsanforderungen sowie dem Entwurf des E/E/PE-Systems, der Testbarkeit sowie des Zusammenhangs der System- und Anwenderdokumentation.

Validierungsplanung

Entwurf und Validierung gehen Hand in Hand und erfolgen zeitgleich. Ziel ist durch Festlegen technischer Verfahren, einen Nachweis erbringen zu können, dass das sicherheitsbezogene E/E/PE-System die spezifizierten Anforderungen an die Sicherheit und an den Entwurf erfüllt. Dabei sind nach IEC 61508 Teil 2 folgende Punkte bei der Planung zu berücksichtigen:

- alle Anforderungen an die Sicherheit und Entwurf

- Validierungsverfahren zum Nachweis der korrekten Implementierung der Sicherheitsfunktion mit pass/fail-Kriterien der Testfälle

- Validierungsverfahren zum Nachweis der erreichten Sicherheitsintegrität mit pass/fail-Kriterien der Testfälle

- Testumgebung, Testwerkzeuge und Betriebsmittel ggf. mit Kalibrierdaten/Zertifikat

- Testbewertungsverfahren

- Testverfahren sowie Bewertungskriterien im Hinblick auf die Validierung der elektromagnetischen Störfestigkeitsgrenzwerte

- Vorgehen zur Behandlung von Ausfällen während der Validierung

Insbesondere wird das Testinterface und dessen Leistungsfähigkeit bzw. die Leistungsfähigkeit der Testumgebung bereits während der Anforderungsspezifikation spezifiziert. Oft ist z.B. eine Fehlerinjektion kaum möglich oder nur mit enormen Aufwand.

Entwurf und Entwicklung – ein Technisches Sicherheitskonzept entsteht

Hauptgegenstand jeder sicherheitsrelevanten Entwicklung ist ein Technisches Sicherheitskonzept. Dessen Entwicklung erfolgt in dieser Phase nach den bereits in der Vorphase spezifizierten Anforderungen an den Entwurf des E/E/PE-Systems. Dabei ist ganzheitlich die Hardwarearchitektur, Softwarearchitektur Embedded-Software, Anwendungssoftware, Datensätze, Sensoren, Aktoren und programmierbare Elektronik passend für die folgenden Anforderungen zu entwerfen / auszuwählen:

- Konformität der Hardwaresicherheitsintegrität (Architekturbeschränkungen und Quantifizierungsrandbedingungen wie Ausfallraten, Diagnosedeckungsgrade, Anteile sicherer Fehler usw…) durch einer der folgenden Pfade:

- 1H mit Hardwarefehlertoleranz (HFT) und dem Anteil sicherer Ausfälle SFF (FMEDA erforderlich), welche mit Ausfallraten mit einem Konfidenzniveau von mind. 70% ermittelt werden können oder

- 2H mit Hardwarefehlertoleranz (HFT), Zuverlässigkeitsdaten aus dem Feld mit 90% Konfidenzniveau und einer konservativen SIL-orientierten HFT-Vorgabe.

- ggf. On-Chip-Redundanz mit besonderen Architekturanforderungen bei Mehrkanal-Strukturen mit kritischen CCF-Faktoren (s. IEC 61508 Teil 2 Anhang E)

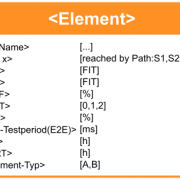

- Konformität der systematischen Sicherheitsintegrität der Software / systematischen Eignung durch einen der folgenden Pfade (S1, S2, S3):

- Erfüllung der Anforderungen an die Vermeidung und Beherrschung von systematischen Fehlern nach IEC 61508 Teil 3

- Betriebsbewährtheit für Betriebsmittel

- Wiederverwendung eines existierenden Software-Elements, welches:

- Betriebsbewährt ist nach IEC 61508 Teil 2 Abschnitt 7.4.10 oder

- Konformität zur IEC 61508 Teil 3 dafür nachgewiesen ist oder

- eine Beurteilung nach den Maßstäben der IEC 61508 Teil 3 Abschnitt 7.4.2.13 für nicht konform entwickelte Elemente durchgeführt wird mit positiven Ergebniss

- und zusätzlich ein Sicherheitshandbuch für dieses Software-Element vorliegt

- Systemfehlerreaktion

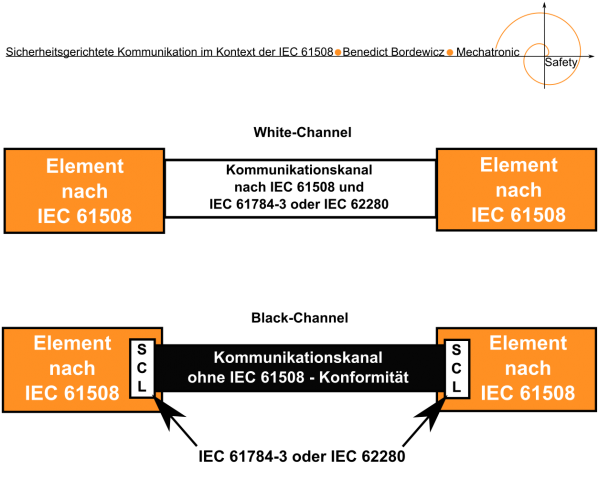

- Datenkommunikationsprozess

- Wechselwirkungsfreiheit / Unabhängigkeit zwischen Softwareelementen mit Sicherheitsbezug und nicht sicherheitsrelevanten Funktionen oder unterschiedlichen Sicherheitsfunktionen mit unterschiedlicher Sicherheitsintegrität

Letzterer Punkt ist oft kritisch in Bezug auf die eine positiv abschließende Beurteilung zur Funktionalen Sicherheit. Eine „geschlossene Argumentation“ für die Funktionale Sicherheit wäre unmöglich. Ein Technisches Sicherheitskonzept zeigt i.d.R. eine strenge Trennung zu nicht sicherheitsrelevanten Funktionen mit Maßnahmen zur Unabhängigkeit wie Partitionierung. Alternativ ist ein Nachweis zu erbringen, dass ein Ausfall einer Nichtsicherheitsfunktion keinen gefährlichen Ausfall einer Sicherheitsfunktion verursacht. Generell ist es empfehlenswert, keine weiteren Funktionen neben der Sicherheitsfunktion in einem sicherheitsbezogenen E/E/PE-System zu implementieren.

Jedes sicherheitsbezogene E/E/PE-System muss nach dem SIL der auf dem System ausgeführten höchsten Sicherheitsintegrität einer Sicherheitsfunktion entwickelt werden. Wenn mehrere Sicherheitsfunktionen auf einen System implementiert werden, kann es notwendig sein, dass ein höherer SIL für das System erforderlich ist, um die Unabhängigkeit sicherzustellen. Dies wird auch als Koexistenzkriterium bezeichnet. Insbesondere für den Ausfall gemeinsamer Ursache ist dieses Kriterium argumentativ ausschlaggebend in der Beurteilung. SIL 2 + SIL 2 wäre dann z.B. SIL 3 auf Systemebene für die Hard- und Software wie z.B. das gemeinsame Betriebssystem.

Ein Technisches Sicherheitskonzept mit Wechselwirkungsfreiheit bedingt Unabhängigkeit

Die Unabhängigkeit in den Dimensionen Zeit, Wert und Raum ist vorwiegend durch gemeinsam genutzte Ressourcen schwer zu erreichen. Die erforderliche Analyse zu diesen abhängigen Ausfällen (z.B. FMECA) ist umfangreich und bildet die Grundlage zur Auswahl der Methode wie z.B. Partitionierung. Ein Technisches Sicherheitskonzept beinhaltet dieses Kapselungsmerkmal i.d.R. als Funktion mit dem höchsten SIL. Beispielsweise sind ein Core-Exception-Interrupt oder ein Fehler im Round-Robin-Logiksystem einer gemeinsam genutzen Ressource wie z.B. einer ADC-Peripherie schwer zu behandeln. Der sichere Zustand der Maschine und systemische Abhängigkeiten der Sicherheitsfunktionen in bestimmten Betriebarten spielen dabei eine entscheidende Rolle. Ein Technisches Sicherheitskonzept mit temporären und/oder verteilten Redundanzen kann erforderlich werden. Dies erzeugt unnötige Komplexität. Die Realisierung dieser Merkmale erfolgt meist im Kontext rechenintensiver Sicherheitsfunktionen wie z.B. Fahrerassistenzsystemem in vernetzten Multi-Core-System-Umgebungen und diese erfordern komplexe Fehlermodelle und erzeugen somit enorme Analysekosten. Daher ist eine Bewertung der Angemessenheit im Entwurf der Sicherheitsfunkionen, deren Anforderungen an die Sicherheitsintegrität des sicherheitsbezogenen E/E/PE-Systems und der Betriebsmittel sowie der Interaktion mit dem Menschen erforderlich.

Ein Argumentieren mit Merkmalen der Unabhängigkeit ist oft die besser Wahl als der Weg über Analysen mit ungewissen Ausgang zum Projektende.

Der Teufel im Entwurf steckt häufig im Detail der ausgewählten Technologie. Ein gutes Technisches Sicherheitskonzept ist dahingehend technologiespezifisch. Die Komplexität im Entwurf und in der Entwicklung ist durch Modularisierung und ganzheitliche Lösungen auf angemessenen Niveau zu halten. Komplexe Technologien erfordern oft ein komplexes Technisches Sicherheitskonzept, welches beherrschbar umzusetzen ist und keine systematischen Fehler fördert. Im Entwurf lässt sich mit „Architekturpattern“ ein gutes Mittelmaß erreichen. Die Verifikationsaktivitäten können mehr als propotional zur Komplexität ausufern. Daher ist die Granularität und Zuordnung der Teilfunktionen auf Subsysteme und mehrere Elemente in der Vorphase entscheidend. Dies bildet die Grundlage zum modularen Entwurf.

Komplexe Hardware-Software-Wechselwirkungen sind während des Entwurfs zu analysieren und zu bewerten und dazu ggf. Maßnahmen zu entwerfen z.B. gegen unbeabsichtigte Funktionalitäten. Oft werden überdimensionierte Elemente ausgewählt, welche der Sicherheitsintegrität nicht gerade förderlich sind (z.B. CPLD statt Safety-zertifizierter µC oder einfache Elektronik mit Testeinrichtung).

FPGA-Strukturen sind z.B. vorteilhaft bei geforderter Diversität zur Vermeidung und Beherrschung von systematischen Fehlern in mehrkanaligen rechenintensiven Strukturen in Kombination mit anderen programmierbaren Logiksystem wie ein µC oder ein SoC für den Anwendungsfall. Der deterministische Nachweis zur Einhaltung der Fehlertoleranzzeit in FPGAs ist ungleich komplexer als in CPLD-Technologie. Weiterhin ist das Ausfallverhalten aufgrund der unterschiedlichen Speichertechnologien zu berücksichtigen. CPLDs verwenden nicht flüchtigen EEPROM, während FPGAs vorwiegend SRAM verwendet, welches nach Verlust der Energie neu geladen werden muss.

Der Erhalt des sicheren Zustands und das Erreichen des sicheren Zustandes kann durch komplexe Technologien erschwert werden. Daher ist es oft notwendig, die Sicherheitsintegrität für ein Element durch ein anderes Element abzusichern (z.B. µC und externer Watchdog mit Frage & Antwort-Sequenzen als Teil einer Programmablaufkontrolle mit externen Abschaltpfad). Die Hardware-Sicherheitsintegrität ist ganzheitlich zu betrachten. Dabei sind meist mehrere Ebenen im Sinne einer fehlertoleranten Architektur erforderlich. Ein technisches Sicherheitskonzept mit 3 Ebenen (Funktionsebene, Diagnosebene, Überwachungsebene der Funktion der Diagnoseebene mit eigenen Abschaltpfad) ist meist für Fail-Safe-Anwendungen ausreichend.

Technisches Sicherheitskonzept im Entwurf – Designanalyse

Der Entwurf ausgehend von der zerlegten Sicherheitsfunktion auf die Elemente des Systems mit Auswahl der Technologien erfordert nach dem Erstentwurf eine Designanalyse im Hinblick auf die Ausfälle der Elemente. Die Fähigkeit zur Fehlertoleranz und Fehlervermeidung ist technologieabhängig. Das System muss im Ganzen in der Lage sein, die erforderliche Intergität zu gewährleisten und bei Verlust dieser Integrität das System in den sicheren Zustand bringen. Ein Technisches Sicherheitskonzept berücksichtigt dies.

Wenn Sie Zweifel haben an der Eignung Ihrer Technologie für Sicherheitsanwendungen, lassen Sie eine Technologiebetrachtung durchführen, um Risiken im Projektverlauf zu vermeiden.

Beispielhaft sei eine „Safe Torque Off“ Sicherheitsfunktion genannt. I.d.R. werden Leistungshalbleiter in einer Leistungsstufe (z.B. 3 Phasen B6 MOSFET oder IGBT Brückenkonfiguration) durch einen µC oder DSP angesteuert. Die Leistungsstufe wandelt Energie (Gleichstrom aus dem DC-Zwischenkreis) in ein Satz drehfelderzeugender Energiesignale auf 3 Phasen für einen elektromagnetischen Wandler (E-Motor) einer bestimmten Technologie (Synchron, Asynchron oder Permanent Magnet Synchronmotor oder Reluktanz). Dabei kann z.B. ein Phasenschluss, Kurzschluss oder ein Fehler in der Ansteuerungselektronik in der Leistungsstufe ein potenziell gefährliches Drehmoment erzeugen, welcher durch die Sicherheitsfunktion behandelt werden soll. Wenn nun die normale Umrichterfunktion Ansteuerungssignale an diese Leistungsstufe sendet, um ein Drehmoment zu erzeugen, die Sicherheitsfunktion jedoch aktiv dies verhindern muss, so darf z.B. die Sicherheitsfunktion bei einen Core-Exception-Interrupt durch ein Ereignis nicht deaktiviert werden.

Daher ist es erforderlich die Leistungsstufe durch eine anderes Element wie z.B. ein Hardwareabschaltpfad im sicheren Zustand zu halten. Dieser Abschaltmechanismus muss auch mit der erforderlichen EMV-Störfestigkeit aufweisen. Ein Isolationsfehler in dem elektromagnetischen Wandler mit der Folge eines Fehlmoments durch magnetische Asymmetrie kann zu einen EMV-Störfeld im Erdungssystem führen und auf den DC-Zwischenkreis rückwirken. Daher ist Kapselung, Isolation, räumlichen Trennung, Trennung von Energieversorgung, Teilung und Überwachung von Teilfunktionen oder Unterlastung/Überdimensionierung auch abhängig von der Technologie, der Entwicklung und der Erfahrung sowie den Analysetätigkeiten (Produkt- und Design-FMEA oder FTA).

Der Entwurf des sicherheitsbezogenen E/E/PE-Systems ist nur mit ausreichend Technologiekenntnis zu beginnen und iterativ mit den Zielen zur Sicherheitsintegrität zu überarbeiten.

Das Konzept der systematischen Eignung für Elemente

Jede Technologie, jedes Element, welches der Technologie zugrunde liegt, kann unterschiedlich systematisch geeignet sein für die zu entwickelnde Sicherheitsfunktion. Eine Software-Lib kann eine Funktion ggf. schlechter im Sinne der Sicherheitsintegrität erfüllen als ein Hardwareelement. Die Kombination mehrerer Elemente mit Unabhängigkeit und/oder technologischer bzw. funktionaler Diversität kann eine bessere systematischen Eignung bilden als jedes Einzelelement. Ein Technisches Sicherheitskonzept enthält eine Kombination von Elementen, auch als Synthese bezeichnet.

Die IEC 61508 gibt in Teil 2 Abschnitt 7.4.3 den Elementen im Sinne ihrer systematischen Eignung die Bezeichnung SC 1 bis 3. Wobei dem Element eine Einfachfehlersicherheit im systematischen Sinne in Bezug auf die Sicherheitsfunktion zugesprochen werden müsste. Wenn es nun zu einer Kombination zweier unabhängiger technologisch diversitärer Elemente z.B. mit SC 2 kommen kann, so bildet diese Kombination die nächst höhere Stufe der systematischen Eignung. In diesem Fall SC 2 für Element A + SC 2 Für Element B ergibt ein SC 3 für die Element-Kombination A+B. Die Elementkombination kann jedoch nicht Grundlage weiterer Kombinationen werden. Es gilt nur SC N +1.

Die Unabhängigkeit muss in einer Analyse gemeinsamer Uraschen nachgewiesen werden in Hinblick auf die Umwelt der unabhängigen Elemente sowie in Entwurf, Realisierung, Betrieb und Instandhaltung. Neben der funktionalen und technologischen Diversität müssen gemeinsame Dienste (z.B. Speicher, ADC, Energieversorgung, gemeinsame Ansteuerungslogik) und Verfahren (z.B. Compiler, Testeinrichtung, Testumgebung) vermieden werden. Zwangsläufig kommt es häufig zu mindestens einen Berührpunkt im Ausführungsverhalten, welcher jedoch nicht gefahrbringend sein darf.

Softwarelemente sind z.B. unabhängig, wenn diese in Raum und Zeit sowie bei Verletzung der Unabhängigkeit diesen Umstand auch Beherrschen können. Wenn eine Funktion in Software den Zugriff auf eine gemeinsame Ressource versperrt und dies erkannt wird aber nicht gehandelt werden kann, da die andere Funktion weitere Ressourcen sperrt, so ist die Beherrschung dieser Art von Integritätsverletzung nicht ausreichend. Eine Integritätsverletzung ist nicht immer gleich ein gefahrbringeder Ausfall, sondern ein potenziell gefährlicher Zustand, welcher zu einen gefahrbringenden Ausfall führen wird.

Zukünftige Technologien werden vermehrt Funktionen in Software ausführen. Dies wird dazu führen, dass die Gestalter neuer Technologien den Umgang mit dem Thema „systematische Sicherheitsintegrität“ als Teil der Unternehmung, der Unternehmenskultur und als kritischen Erfolgsfaktor behandeln müssen!

Hardwaresicherheitsintegrität – architekturbestimmenden Faktoren (HFT, SFF, Bauteilgüte)

Die Hardware bildet den Kern des sicherheitsbezogenen Systems. Ohne funktionierende Hardware kann die Software nicht funktionieren. Die Sicherheitsintegrität der Hardware ist abhängig von Ihrer Güte (Ausfallwahrscheinlichkeit) sowie der Architektur mit Merkmalen wie Fehlertoleranz und Fehlerbeherrschung im Technischen Sicherheitskonzept. Dabei ist es Ziel, eine Hardwareachitektur zu entwerfen, welche die spezifizierten Anforderungen zur Integrität erfüllt und dabei den erforderlichen Ausfallgrenzwert der Sicherheitsfunktion nicht überschreitet.

Ein Technisches Sicherheitskonzept berücksichtigt die erforderliche Hardwareintegrität!

Die Hardware wird beschränkt angesehen in ihrer Sicherheitsintegrität. Zum einen ist die Ausfallrate der Bauteile beschränkend zum anderen ist die Komplexität bestimmter Elementtypen in Fehlermodellen nicht zu 100% analytisch erfassbar. Daher bildet das Zuverlässigkeitsmodell eine Abschätzung zur Robustheit der Hardware gegenüber Fehlern und Ausfall. In Kombination mit der Vorhersage zur Ausfallwahrscheinlichkeit bildet die Hardwarefehlertoleranz (HFT) den bestimmenden Faktor zur Struktur der Hardwarearchitektur im Hinblick auf die Kanäle und Testeinrichtungen (Diagnosefunktionen). In anwendungsspezifischen FuSi-Normen wie der ISO 13849 Teil 1 findet sich daher das Konzept der vorgesehenden Architekturen, dort auch bezeichnet als Kategorien.

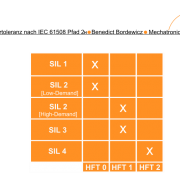

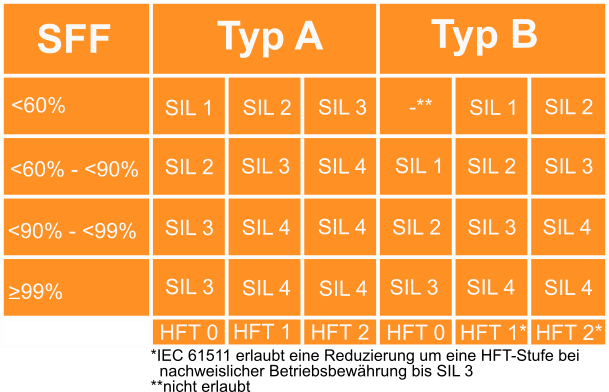

Die IEC 61508 zeigt in Teil 2 Abschnitt 7.4.4 zwei mögliche Pfade im Hinblick auf Architekturbeschränkungen durch die Hardware-Sicherheitsintegrität. Bei der Wahl des Pfades ist der Sektor und die Anwendung maßgeblich (sichere Zustand, Redundanzmöglichkeiten und Reparaturzeitdauer oder Intervall (MTTR) im Verhältnis zur Wiederholungsprüfung, Determinismus). Grob lässt sich sagen, dass es entweder den Pfad für betriebsbewährte und deterministisch bestimmte Architekturen gibt oder den probalilistischen Weg. Beide Wege setzen auf die Hardwarefehlertoleranz jedoch mit unterschiedlicher Beziehung zur Quantifizierung. Letzter genannter Pfad (s. IEC 61508 Teil 2 Abschnitt 7.4.4 „1H“) ist i.d.R. die typische Entwicklung neuer Technologien geeignet und wird im Folgenden weiter im Detail vorgestellt. Ein Technisches Sicherheitskonzept folgt einem der beiden Pfade. Der alternative Pfad 2H ist in der folgenden Tabelle vereinfacht dargestellt.

Durch Begründung kann die HFT im Pfad 2H um eine Stufe reduziert werden wie es z.B. in der IEC 61511 der Fall ist für betriebsbewährte Elemente oder durch andere Fehlertoleranzmaßnahmen wie z.B. ein virtueller Sensor. Weiterhin sind Felddaten zur Ermittlung von Ausfallraten nach annerkannten Normen zu sammeln, auszuwerten und deren Konfidenzintervall abzuschätzen bis eine Konfidenz größer 90 % vorliegt zum erreichten Ausfallgrenzwert (PFH). Weiterhin ist der Einsatz von Typ B Elementen nur mit mehr als 60% DC möglich.

Der Element-Typ bestimmt die Hardwarearchitektur!

Die IEC 61508 unterscheidet Elemente in Typ A und Typ B, welche für die Sicherheitsfunktion bedeutsam sind. Ein Typ A Element ist vollständig in seinem Ausfallverhalten und Verhalten unter Fehlbedingungen definiert und mit verlässlichen Ausfallraten beschrieben. Ein Typ B Element ist unvollständig beschrieben in seinem Ausfallverhalten und weist Ausfallraten mit geringen Konfidenzniveau auf.

Beispiele für Typ A Elemente (einfache Betriebsmittel) sind:

- elektronische Leistungshalbleiter (MOSFET/IGBT)

- Relais, Ventil etc…

Beispiele für Typ B Elemente (komplexe Betriebsmittel) sind:

- HF-Frontend ohne Hersteller-FMEA

- SOC, FPGA, µC

Sind die Elementtypen identifiziert, so erfolgt eine Abschätzung der Anteile sicherer Ausfälle für jedes Element. Weiterhin ist die Anordnung dieser Elemente unterschiedlichen oder gleichen Typs zur Erfüllung der Sicherheitsintegrität architekturbestimmend. Bei einer Reihenanordnung bestimmt das schwächste Element die erreichbare Sicherheitsintegrität (Vgl. Kette mit schwächsten Kettenglied). Bei der Parallelanordnung mit Unabhängigkeit kann sogar ein SIL X + N erreicht werden, wobei X das SIL eines Elements mit dem höchsten SIL ist und N die HFT ist (HFT=N=1, wenn 2 Elemente parallel angeordnet sind , HFT=N=2 wenn 3 Elemente parallel sind usw…). Die Sicherheitsintegrität der Hardware ist jedoch auf Systemebene durch die sytematische Eignung eines Elements (SC) begrenzt auf SC N +1. Diese Methoden zur Kombination von Elementen in Teilsystemen, welche wiederum die Gesamtheit des sicherheitsbezogenen E/E/PE-Systems bilden, sind Kern der Entwurfphase und bilden die Grundlage zur Realisierung der erforderlichen Hardware-Sicherheitsintegrität in Wechselwirkung mit der systematischen Eignung. Ein Technisches Sicherheitskonzept baut auf dieser Grundlage auf.

Die Funktionsstruktur bzw. die mögliche Anordnung und Kombination der Elemente, die Güte der Bauteile, die Ausfallart der Gesamtheit aller Elemente und die Element-Komplexität bestimmen die Hardwearesicherheitsintegrität und damit das Vertrauen in die Robustheit der Hardwarearchitektur. Kernelement der Hardwaresicherheitsintegrität sind Ausfallraten und Hardwarefehlertoleranzmaßnahmen, welche die HFT bestimmen.

Es ist jedoch zu berücksichtigen, dass die systematische Leistungsfähigkeit eines Elements den erreichbaren SIL durch die systematische Sicherheitsintegrität begrenzt. Eine Sicherheitsfunktion mit SIL 3 kann aus zwei unabhängigen Elementen mit SIL 2 bzw. SC 2 bestehen, jedoch muss die Entwicklung die systematische Leistungsfähigkeit eines SIL 3 aufweisen. Dies kann durch Diversität wie z.B. unterschiedliche Hersteller der Elemente oder unterschiedliche Technologien sichergestellt werden.

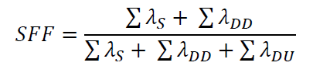

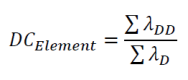

Anteil sicherer Ausfälle bestimmen (SFF)

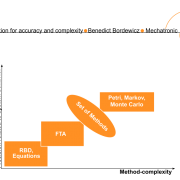

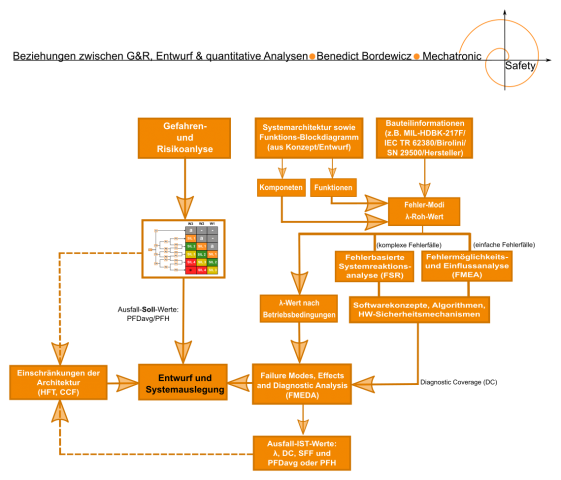

Ein Zuverlässigkeitsmodell zur quantitativen Analyse muss entwickelt werden. Dazu ist eine Methode zur Modellierung auszuwählen. Meisst wird eine FMEDA durchgeführt. Input sind mindestens eine Blockarchitektur mit allen Schnittstellen, die Schaltpläne der Blöcke, Ausfallraten aus einer Bauteil-Ausfallratendatenbank und mögliche detaillierte Fehlermodelle zu spezifischen Bauteilausfallraten. Weitere Bauteil und Betriebsdaten wie Temperatur, Zyklen, Spannung, Strom, Technologie (z.B. CMOS, TLL), Lebensdauer/Betriebsdauer, Auslegung (über/unterdimensioniert) müssen vorliegen. Output dieser Analysen sind sicherheitstechnische Kennzahlen der Architektur zur Sicherheitsintegrität wie der Anteil sicherer Ausfälle (SFF = Safe Failure Fraction) oder die Eigendiagnosefähigkeit der betrachteten Elemente (Diagnosedeckungsgrad, DC = Diagnostic Coverage) sowie die Teilwerte zur Ausfallwahrscheinlichkeit der Sicherheitsfunktion (PFH/PFDavg). Im Entwurf ist eine grobe Schätzung mit einfachen Methoden bzw. Verfahren sinnvoll. Da im weiteren Verlauf ein passendes Zuverlässigkeitsmodell mit passender Methode entwickelt wird, ist es i.d.R. frühzeit notwendig, ein passendes Verfahren für die Komplexität der Technologie und des Systemverhaltens auszuwählen. Nachfolgend sind grob die Methoden bzw. Verfahren in Ihrer Genauigkeit und der Komplexität aufgetragen:

Bei der Bestimmung der SFF ist bei Elementen mit HFT = 0 im High-Demand-Mode der Faktor Zeit (Diagnoseintervall bzw. Testrate) zu berücksichtigen. Ist z.B. die Diagnosetestrate kleiner dem 100-Fachen der Anforderungsrate der Sicherheitsfunktion, so ist die Diagnose als unwirksam in der Analyse zur SFF zu betrachten. Gleiches Gilt für das Verhältnis von Diagnoseintervall zur Fehler- bzw. Prozesstoleranzzeit. Wenn nur alle 200 ms die Diagnose ausgeführt wird und der Übergang zum sicheren Zustand weitere 400 ms benötigt, es jedoch im Fehlerfall bereits nach 500 ms zu Gefährdungen kommt, so ist die Diagnose auch hier in der Analyse zur SFF als unwirksam zu betrachten.

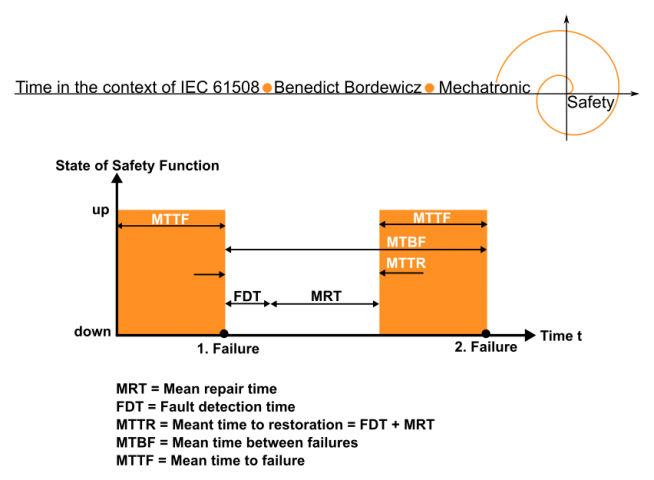

Bei Elementen welche Sicherheitsfunktionen ausführen mit HFT > 0 im High-Demand-Mode oder Sicherheitsfunktionen im Low-Demand-Mode muss das Diagnoseintervall + Reparaturzeit kleiner als die MTTR sein.

Fehrlertoleranzmechanismen in einer einkanaligen Architektur können die Ausführungsqualität der bestimmungsgemäßen Funktion negativ beeinträchtigen wie z.B. mehrere in Serie geschaltete Dioden mit ihren parasitären Kapazitäten an einem Signaleingang für ein Winkelsensor für eine Safe-Torque-Off-(STO)-Sicherheitsfunktion welcher auch für ein Lageregelkreis verwendet würde und dessen Dynamikbereich einschränken könnte.